# Fundamentals of microelectronics processes

### Chang Liu ME Northwestern University

# Several aspects of processing

- Chemistry and physics of the process

- Process variables and figure of merits

- Machine operation procedure safety

- Principle of machine operation and machine parts

- Vendors and pricing of machine, parts, supplies

- Electronic and mechanical subsystems of machine

- Supplies for the process

- Safety precautions and potential hazards

- Process behavior with materials and wafers

- Rate

- Uniformity

- Repeatability

- Temperature or chemical stability

- Peculiarities (how does the process work differently after so and so worked on it before you ☺).

- Jargons

### Metalization

- Sputtering

- Evaporation

- Electron beam evaporation

- Thermal evaporation

- Electroplating

- Electroless plating

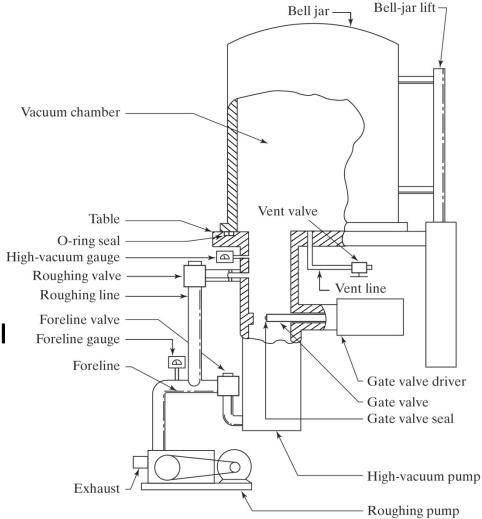

# **General Vacuum Equipment Parts**

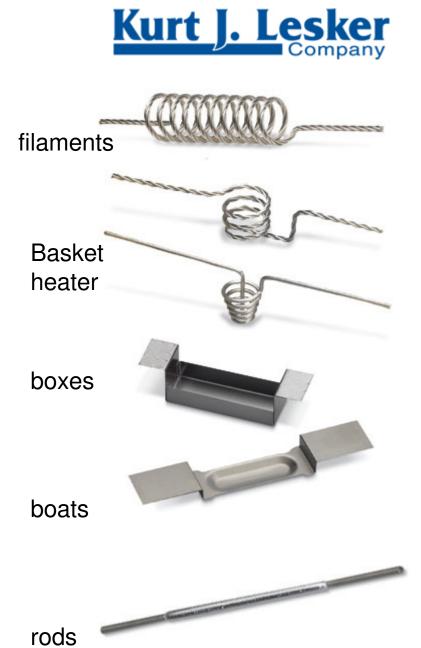

- Deposition sources

- Evaporation chamber

- Vacuum pumps

- Roughing pumps

- High vacuum pumps

- Deposition rate monitor

### Vacuum Jargon

- 1 ATM=760 torr

- 1 pascal =  $1 \text{ N/m}^2$

- 1 torr= 133.322 Pascals

| Pressure Units |                      |                                |                         |                                    |                         |                                         |  |  |  |  |  |

|----------------|----------------------|--------------------------------|-------------------------|------------------------------------|-------------------------|-----------------------------------------|--|--|--|--|--|

|                | pascal<br>(Pa)       |                                |                         | technical atmosphere<br>(at) (atm) |                         | pound-force per<br>square inch<br>(psi) |  |  |  |  |  |

| 1 Pa           | ≡ 1 N/m <sup>2</sup> | 10 <sup>-5</sup>               | 1.0197×10 <sup>-5</sup> | 9.8692×10 <sup>-6</sup>            | 7.5006×10 <sup>-3</sup> | 145.04×10 <sup>-6</sup>                 |  |  |  |  |  |

| 1 bar          | 100,000              | $\equiv 10^6 \text{ dyn/cm}^2$ | 1.0197                  | 0.98692                            | 750.06                  | 14.5037744                              |  |  |  |  |  |

| 1 at           | 98,066.5             | 0.980665                       | ≡ 1 kgf/cm <sup>2</sup> | 0.96784                            | 735.56                  | 14.223                                  |  |  |  |  |  |

| 1 atm          | 101,325              | 1.01325                        | 1.0332                  | ≡ 1 atm                            | 760                     | 14.696                                  |  |  |  |  |  |

| 1 torr         | 133.322              | 1.3332×10 <sup>-3</sup>        | 1.3595×10 <sup>-3</sup> | 1.3158×10 <sup>-3</sup>            | ≡ 1 Torr; ≈ 1 mmHg      | 19.337×10 <sup>-3</sup>                 |  |  |  |  |  |

| 1 psi          | 6,894.76             | 68.948×10 <sup>-3</sup>        | 70.307×10 <sup>-3</sup> | 68.046×10 <sup>-3</sup>            | 51.715                  | $\equiv 1 \text{ lbf/in}^2$             |  |  |  |  |  |

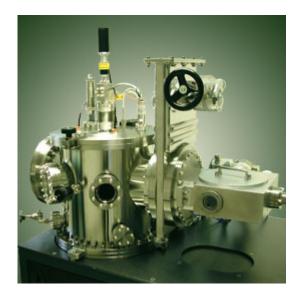

This is a dual e-beam/thermal evaporator for the deposition of Au, Ag, Cu, Ni, Cr, Al, Ti, Fe, Co, W, Gd, Nb, Ta, permalloy, Si, and AL<sub>2</sub>O<sub>3</sub>. 6-pocket electron gun two electrodes for thermal sources wafers from 2" to 6" capacity: 4 wafers cryopumped with a base vacuum of 5E-8T uniformity shield yielding thickness uniformity of 4 % over 4" wafers.

### Vacuum pumps

- Coarse Vacuum 760–1 Torr

- **Rough Vacuum** 760–10<sup>-3</sup> Torr

- **High Vacuum** 10<sup>-4</sup>—10<sup>-8</sup> Torr

- Ultra High Vacuum  $10^{-9}$ – $10^{-12}$  Tor

### How many particles are there?

•

### **Pump Principles**

### **Rotary Vane Pump**

Vacuum Level: Coarse Vacuum or Rough Vacuum (design dependent) Gas Removal Method: Gas Transfer Pump Design: Oil-Sealed (wet)

### Edwards EM series rotary pump

Piston pump Vacuum Level: Rough Vacuum Gas Removal Method: Gas Transfer Pump Design: Dry

> Kinney-tuthill Rotary piston pump

### **Pumping Principles**

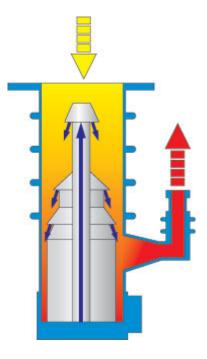

Diffusion pump 10-4-10<sup>-7</sup> torr

Varian DPD series Diffusion pump

Cryogenic pumps

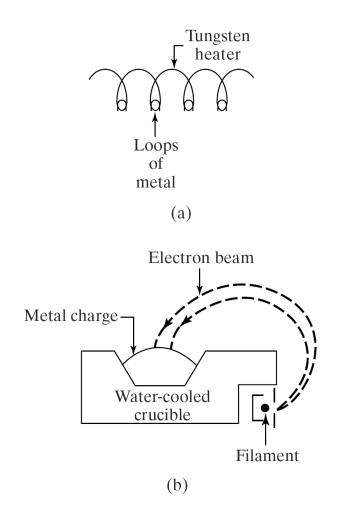

### **Evaporation** Filament & Electron Beam

- (a) Filament Evaporation with Loops of Wire Hanging from a Heated Filament

- (b) Electron Beam isFocused on MetalCharge by a MagneticField

### **Evaporation rate**

### Mean free path of particles

•

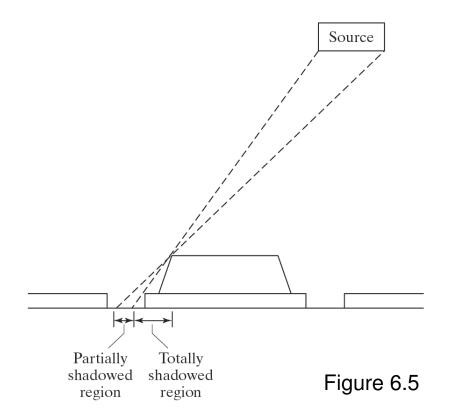

### Evaporation Shadowing and Step Coverage

Shadowing and Step Coverage Problems Can Occur in Low Pressure Vacuum Deposition in which the Mean Free Path is Large

### Types of coverage

Conformal coverage  Non conformal coverage

# Film Deposition Sputtering

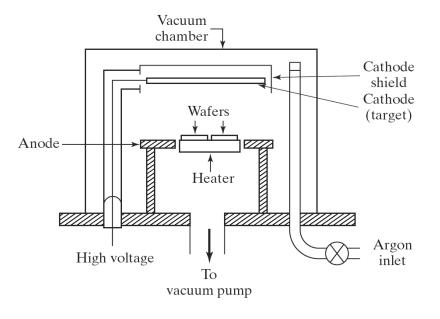

### Figure 6.6

A dc sputtering system in which the target material acts as the cathode of a diode and the wafers are mounted on the system anode.

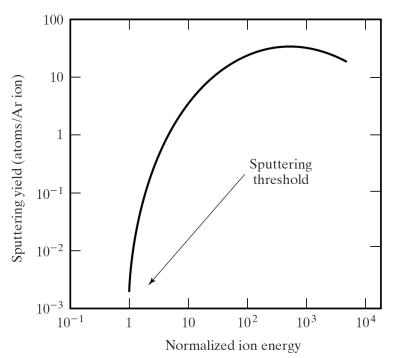

### Figure 6.7 Sputtering vield i

Sputtering yield increases rapidly as ion energy is increased above the sputtering threshold (argon)

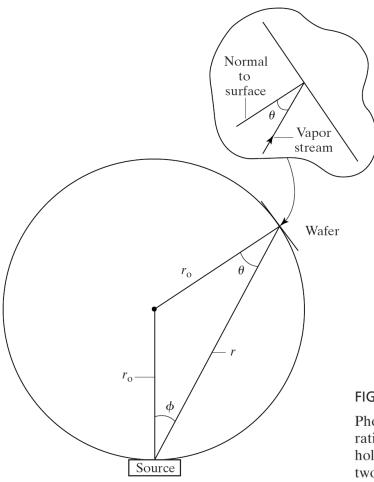

### Evaporation Electron Beam

Growth Rate

$G = \frac{m}{\pi \rho r^2} \cos \phi \cos \theta$

$$\cos\phi = \cos\theta = \frac{r}{2r_o}$$

$$G = \frac{m}{4\pi\rho r_o^2}$$

### FIGURE 6.4

Photograph of a laboratory E-beam evaporation system with a planetary substrate holder which rotates simultaneously around two axes.

### Sputtering

• DC vs. RF

AJA Orion 8

- Metal

- Insulator

- Alloy

- Gas mixture

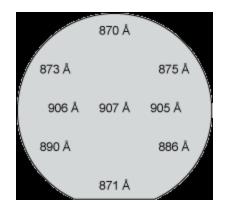

Deposition of SiO(2) on 100mm diameter Si wafer at 150 Watts, 3mTorr, 5.5" working distance. Uniformity is  $\pm$  2.08%

### Typical system components

Substrate heater

Computer control

Vacuum pumps

Targets

### Power distribution modules

Cluster

### Pros and Cons

- Thermal evaporator

- High temperature

- Rapid deposition

- Equipment low cost

- Sputtering

- Low temperature

- Better step coverage

- Equipment

expensive

### Introduction to Microelectronic Fabrication

by

Richard C. Jaeger Distinguished University Professor ECE Department

**Auburn University**

VOLUME V INTRODUCTION TO MICROELECTRONIC FABRICATION SECOND EDITION RICHARD C. JAEGER

Chapter 2 Lithography VOLUME V INTRODUCTION TO MICROELECTRONIC FABRICATION SECOND EDITION RICHARD C. JAEGER

For the exclusive use of adopters of the book Introduction to Microelectronic Fabrication, Second Edition by Richard C. Jaeger. ISBN0-201-44494-1.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

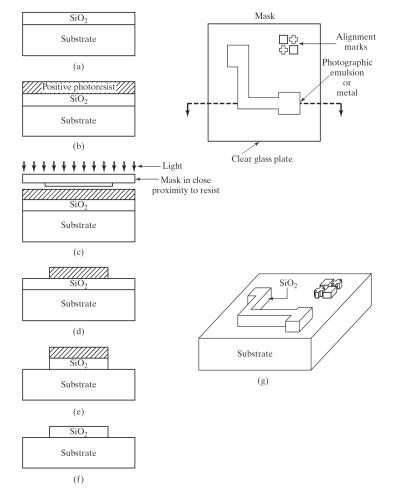

### **Photolithographic Process**

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

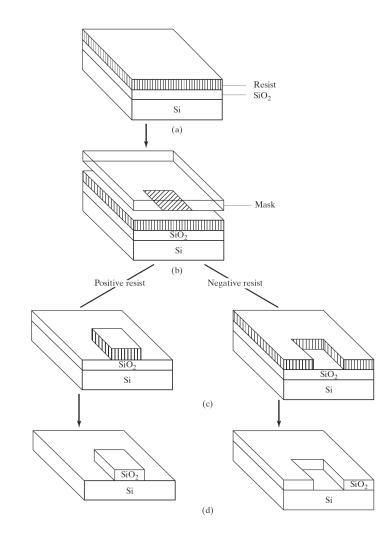

- (a) Substrate covered with silicon dioxide barrier layer

- (b) Positive photoresist applied to wafer surface

- (c) Mask in close proximity to surface

- (d) Substrate following resist exposure and development

- (e) Substrate after etching of oxide layer

- (f) Oxide barrier on surface after resist removal

- (g) View of substrate with silicon dioxide pattern on the surface

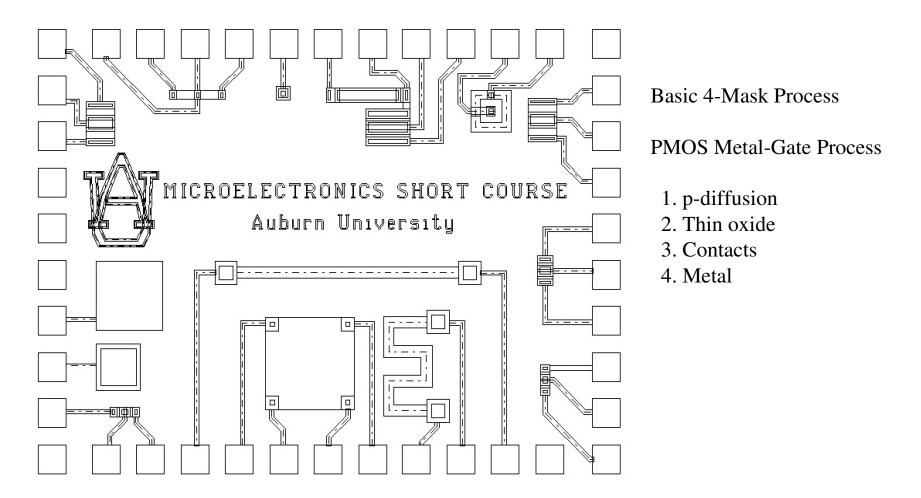

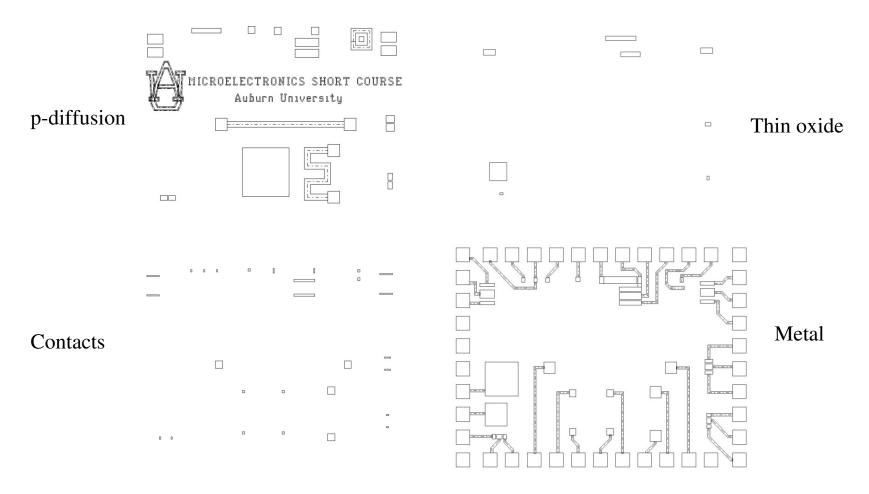

### Photomasks CAD Layout

- Composite drawing of the masks for a simple integrated circuit using a four-mask process

- Drawn with computer layout system

- Complex state-of-the-art CMOS processes may use 25 masks or more

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

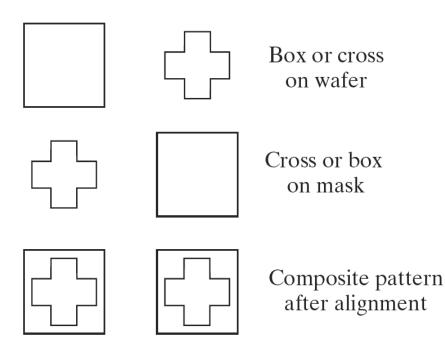

# Mask Alignment

- Each mask must be carefully aligned to the previous levels

- Some form of alignment marks are used

- Automated alignment and exposure in production lines

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

### **ITRS Lithography Projections**

| Table 2.5     ITRS Lithography Projections                                 |            |                            |                                                                                  |                                                                                                     |                                                                   |                                                                                 |  |  |  |  |

|----------------------------------------------------------------------------|------------|----------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Year                                                                       | 2001       | 2003                       | 2005                                                                             | 2008                                                                                                | 2011                                                              | 2014                                                                            |  |  |  |  |

| Dense Line Half-Pitch (nm)                                                 | 150        | 120                        | 100                                                                              | 70                                                                                                  | 50                                                                | 35                                                                              |  |  |  |  |

| Worst Case Alignment Tolerance<br>Mean + 3 $\sigma$ (nm)                   | 52         | 42                         | 35                                                                               | 25                                                                                                  | 20                                                                | 15                                                                              |  |  |  |  |

| Minimum Feature Size F (nm)<br>Microprocessor Gate Width                   | 100        | 80                         | 65                                                                               | 45                                                                                                  | 30                                                                | 20                                                                              |  |  |  |  |

| Critical Dimension Control (nm)<br>Mean + 3 $\sigma$ - Post Etching        | 9          | 8                          | 6                                                                                | 4                                                                                                   | 3                                                                 | 2                                                                               |  |  |  |  |

| Equivalent Oxide Thickness (nm)                                            | 1.5 - 1.9  | 1.5 - 1.9                  | 1.0 - 1.5                                                                        | 0.8 - 1.2                                                                                           | 0.6 - 0.8                                                         | 0.5 - 0.6                                                                       |  |  |  |  |

| Lithography Technology Options                                             | 248 nm DUV | 248 nm + PSM<br>193 nm DUV | 193 nm + PSM<br>157 nm<br>E-beam projection<br>Proximity x-ray<br>Ion Projection | 157 nm +PSM<br>E-beam projection<br>E-beam direct write<br>EUV<br>Ion Projection<br>Proximity x-ray | EUV<br>E-beam projection<br>E-beam direct write<br>Ion Projection | EUV<br>E-beam projection<br>E-beam direct write<br>Ion Projection<br>Innovation |  |  |  |  |

| DUV - deep ultraviolet; EUV - extreme ultraviolet; PSM - phase shift mask; |            |                            |                                                                                  |                                                                                                     |                                                                   |                                                                                 |  |  |  |  |

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

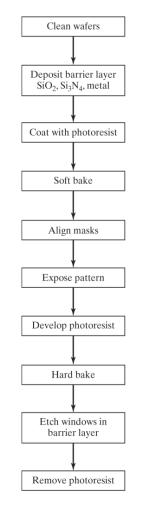

### Photolithographic Process

- Each mask step requires many individual process steps

- Number of masks is a common measure of overall process complexity

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

### Wafer Cleaning

- Wafers must be cleaned of chemical and particulate contamination before photo processing

- Example of "RCA" cleaning procedure in table below

TABLE 2.2

Silicon Wafer Cleaning Procedure<sup>[4,5]</sup>

#### A. Solvent Removal

- 1. Immerse in boiling trichloroethylene (TCE) for 3 min.

- 2. Immerse in boiling acetone for 3 min.

- 3. Immerse in boiling methyl alcohol for 3 min.

- **4.** Wash in DI water for 3 min.

- B. Removal of Residual Organic/Ionic Contamination

- 1. Immerse in a (5:1:1) solution of H<sub>2</sub>O–NH<sub>4</sub>OH–H<sub>2</sub>O<sub>2</sub>; heat solution to 75–80 °C and hold for 10 min.

- 2. Quench the solution under running DI water for 1 min.

- **3.** Wash in DI water for 5 min.

- **C.** Hydrous Oxide Removal

- **1.** Immerse in a (1:50) solution of  $HF-H_2O$  for 15 sec.

- 2. Wash in running DI water with agitation for 30 sec.

- D. Heavy Metal Clean

- 1. Immerse in a (6:1:1) solution of  $H_2O-HCl-H_2O_2$  for 10 min at a temperature of 75–80 °C.

- 2. Quench the solution under running DI water for 1 min.

- 3. Wash in running DI water for 20 min.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

### Piranha Cleaning

- Clean organic residue

- Mix 4:1 H<sub>2</sub>SO<sub>4</sub> (pure or 98%)and H<sub>2</sub>O<sub>2</sub>

Solution will heat up

- Heat up to 100°C

- Fresh piranha solution should bubble

- Dip wafer using Teflon holders or quartz holders

- Hold for a certain time, rinse.

### Photoresist spin coating

- Mechanism

- Thickness control

- Defects (edge beading)

### Photoresist Deposition Automated Production Systems

• Rite Track 88e wafer processing system (Courtesy of Rite Track Services, Inc.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

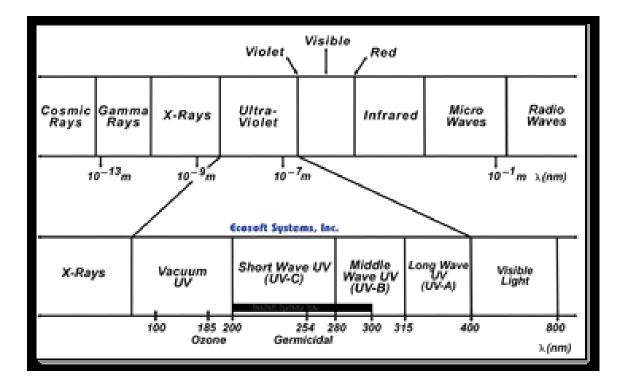

# **Resists for Lithography**

- Resists

- Positive

- Negative

- Exposure Sources

- Light

- Electron beams

- Xray sensitive

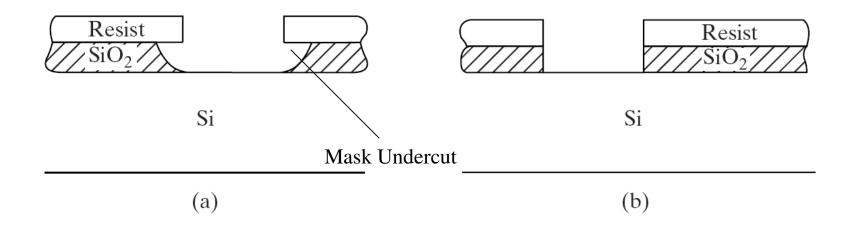

# **Oxide Etching Profiles**

- (a) Isotropic etching wet chemistry mask undercutting

- (b) Anisotropic etching dry etching in plasma or reactive ion etching system

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

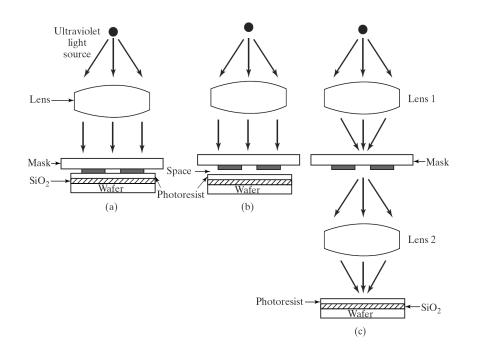

### **Printing Techniques**

- Non-contact exposure

- Light path

management

- Reduction ratio possible

- Stepper

- Large mask

- Contact exposure

- Minimize diffraction

- -1:1

- Contact aligner

- Contamination prone

<sup>© 2002</sup> Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

### **Printing Techniques**

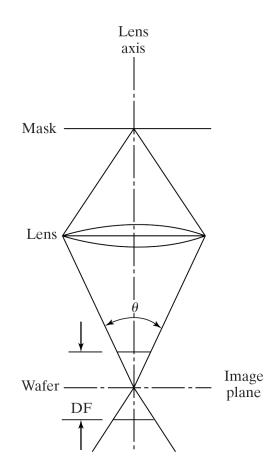

#### FIGURE 2.11

Artist's conception of various printing techniques. (a) Contact printing, in which wafer is in intimate contact with mask; (b) proximity printing, in which wafer and mask are in close proximity; (c) projection printing, in which light source is scanned across the mask and focused on the wafer. Copyright, 1983, Bell Telephone Laboratories, Incorporated. Reprinted by permission from Ref. [5].

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

- Contact printing damages the reticle and limits the number of times the reticle can be used

- Proximity printing eliminates damage

- Projection printing can operate in reduction mode with direct step-onwafer, eliminating the need for the reduction step presented earlier

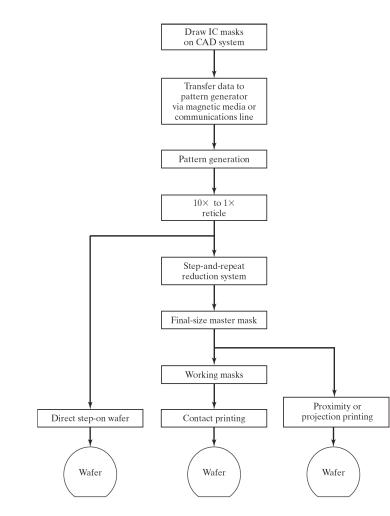

### **Mask Fabrication**

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

- Masking processes

- Direct step on wafer

- Contact printing

- Proximity printing

- Projection printing

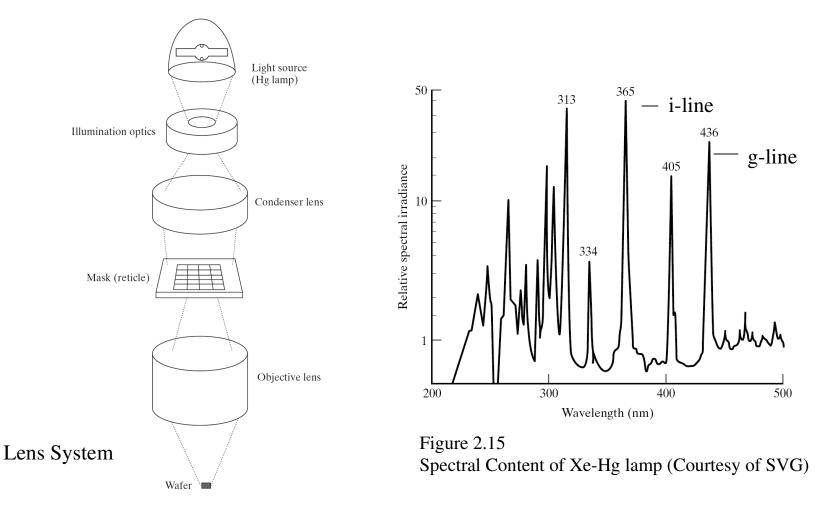

### Wafer Steppers

Figure 2.13 The true complexity of a wafer stepper is apparent in this system drawing. (Courtesy of ASM Lithography, Inc.

- Wafer stepping systems widely used

- Must be completely isolated from sources of vibration

- High degree of environmental control needed

- Often in their own clean room

For the exclusive use of adopters of the book Introduction to Microelectronic Fabrication, Second Edition by Richard C. Jaeger. ISBN0-201-44494-1.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

# Minimum Feature Size and Depth of Field

Minimum Feature Size  $F = 0.5 \frac{\lambda}{NA}$

Depth of Field DF =

$$0.6 \frac{\lambda}{(NA)^2}$$

Numerical Aperture  $NA = \sin \theta$

$\lambda$  = wavelength of exposure source

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

# Wafer Steppers (cont.)

For the exclusive use of adopters of the book Introduction to Microelectronic Fabrication, Second Edition by Richard C. Jaeger. ISBN0-201-44494-1.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

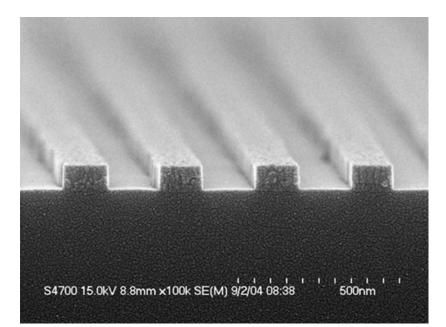

#### **Critical Dimensions**

the width of a patterned line or the distance between two lines, monitored to maintain <u>device</u> performance consistency; that dimension of a specified geometry that must be within design tolerances.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

### Analogy to photography

- Toy Camera

- Small lens, small NA

- Large camera

- Large lens, large NA

For the exclusive use of adopters of the book Introduction to Microelectronic Fabrication, Second Edition by Richard C. Jaeger. ISBN0-201-44494-1.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### Depth of Field

22

f/4

Large DOF

#### Small DOF

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

f/32

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

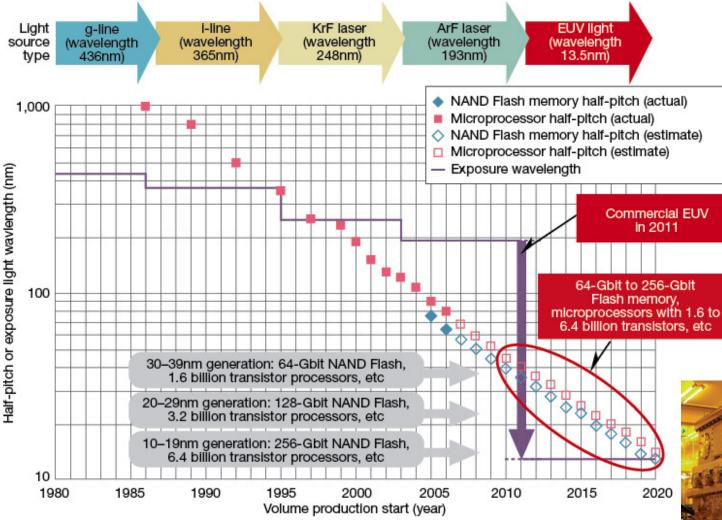

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher. Fig 1 Slashing Lithography Wavelength to Drive Further Geometry Shrink EUV lithography has been pegged as a technology for the future, but it is approaching practical use fast. Diagram by *Nikkei Electronics* based on material from Intel, International Technology Roadmap for Semiconductors (ITRS), etc.

Nikon EUV machine prototype

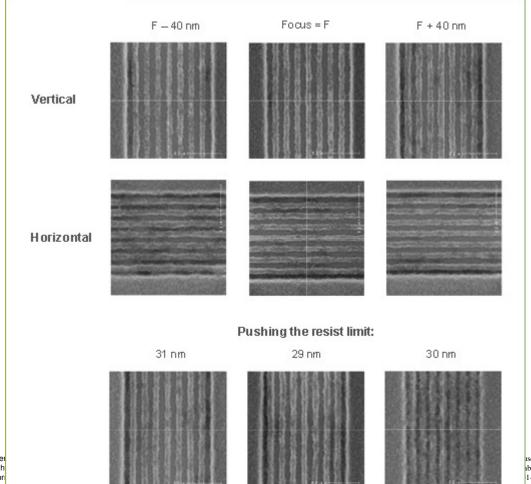

#### **EUV** Capabilities

use of adopters of the book Introduction to ubrication, Second Edition by Richard C. 1-44494-1.

© 2002 Pearson Education, Inc., Upper material is protected under all copyrigh material may be reproduced, in any for from the publisher.

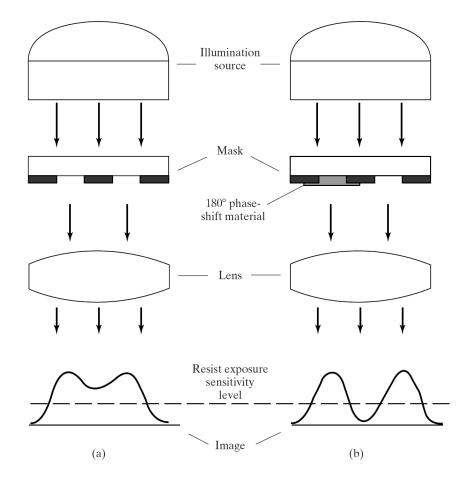

#### Phase Shifting Masks

Pattern transfer of two closely spaced lines

- (a) Conventional masktechnology lines notresolved

- (b) Lines can be resolved with phase-shift technology

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

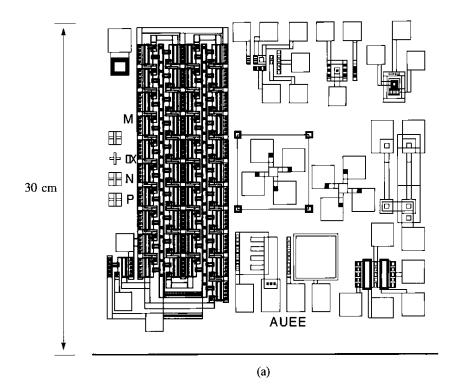

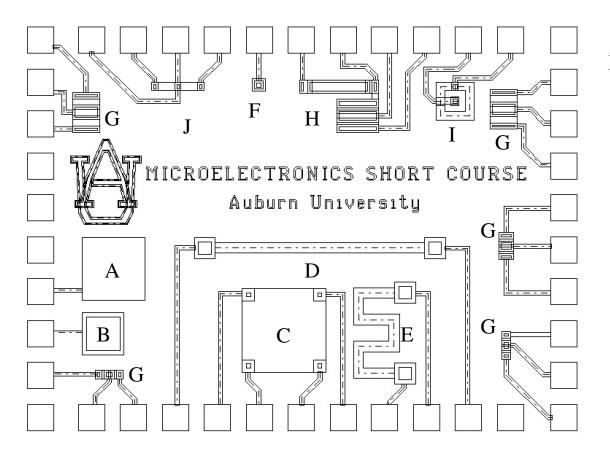

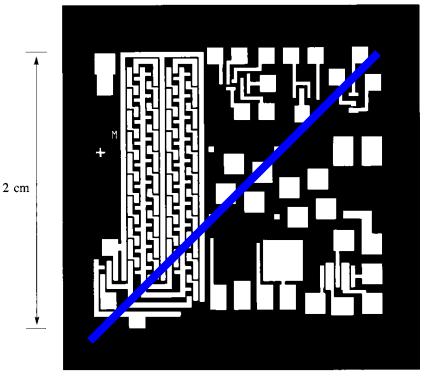

### Layout of a Class Chip

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### Four Mask Class Process

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### Layout of Class Chip

Metal Gate PMOS Process

A. Thick oxide capacitor

B. Thin Oxide Capacitor

C. Van der Pauw structure

D. Resistor 1

E. Resistor 2

F. Diode

G. PMOS transistors

H. PMOS logic inverter

I. Lateral pnp transistor

J. Kelvin contact structure

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

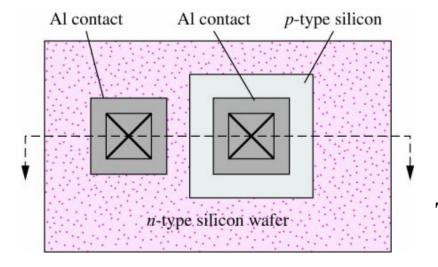

#### Our Class Process Diode & Resistor Fabrication

Top view of an integrated pn diode.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

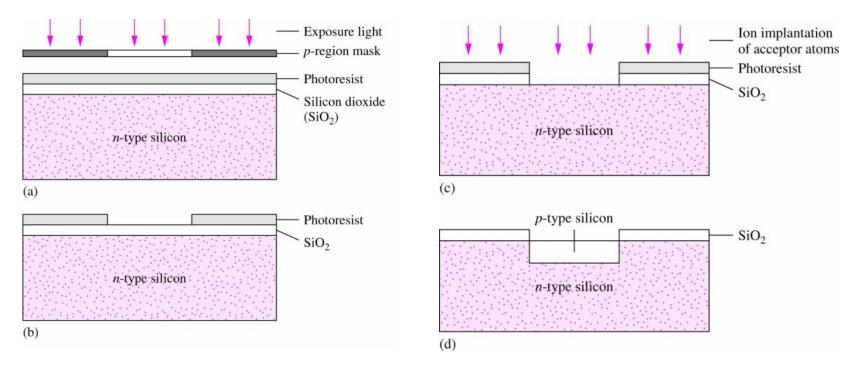

#### Our Class Process Diode Fabrication (cont.)

(a) First mask exposure (b) Post-exposure and development of photoresist(c) After SiO<sub>2</sub> etch (d) After implantation/diffusion of acceptor dopant.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

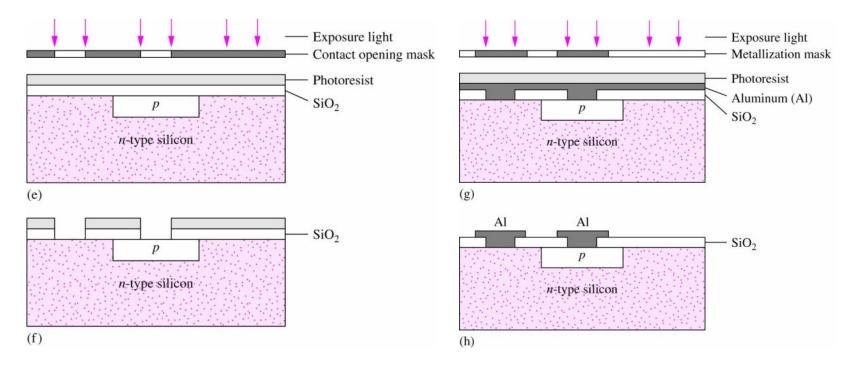

#### Our Class Process Diode Fabrication (cont.)

(e) Exposure of contact opening mask, (f) after resist development and etching of contact openings, (g) exposure of metal mask, and (h) After etching of aluminum and resist removal.

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### Contamination

Human hair at the same scale as the integrated circuit with 10 μm feature size

• Today's feature size 100 nm - 100 times smaller!

(b)

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

#### **Clean Room Specifications**

| Table 2.1                         | Clean Room Ratings by Class of Filtration                                                                           |                                                                        |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Class                             | Number of 0.5-µm<br>particles per ft <sup>3</sup> (m <sup>3</sup> )                                                 | Number of 5-µm<br>particles per ft <sup>3</sup> (m <sup>3</sup> )      |

| 10,000<br>1,000<br>100<br>10<br>1 | $\begin{array}{cccc} 10000 & (350,000) \\ 1000 & (35,000) \\ 100 & (3,500) \\ 10 & (350) \\ 1 & (35)^* \end{array}$ | 65 (23,000)<br>6.5 (2,300)<br>0.65 (230)<br>0.065 (23)<br>0.0065 (2.3) |

\*It is very difficult to measure particulate counts below 10/ft<sup>3</sup>

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

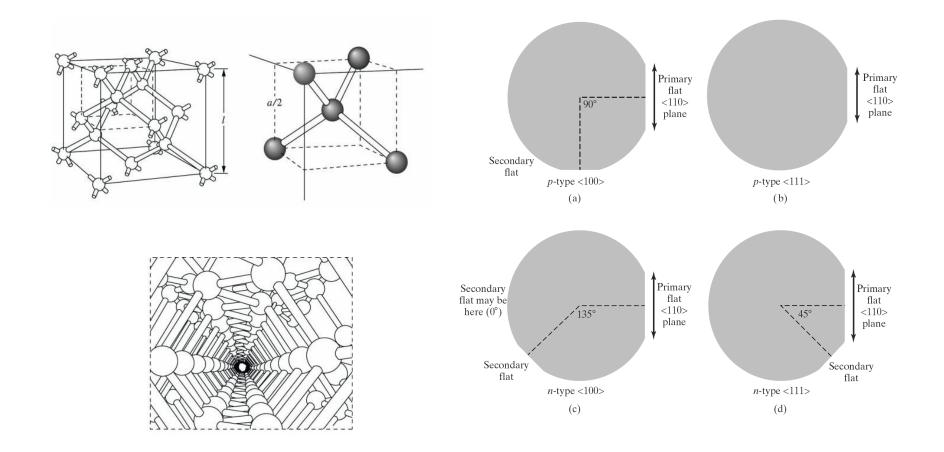

# Common Wafer Surface Orientations

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.

# End of Chapter 2

© 2002 Pearson Education, Inc., Upper Saddle River, NJ. All rights reserved. This material is protected under all copyright laws as they currently exist. No portion of this material may be reproduced, in any form or by any means, without permission in writing from the publisher.